Реферат: Разработка программы на Ассемблере

Реферат: Разработка программы на Ассемблере

7.10 НЕОДНОЗНАЧНОСТЬ ПРЕДСТАВЛЕНИЯ ДВОИЧНЫХ НАБОРОВ

Набор единиц и нулей хранящихся в регистре или ячейке памяти (двоичный набор) для микропроцессора ничего не означает. Пусть в регистре находится набор из восьми битов 10000110. Он может быть интерпретирован следующим образом, как:

1) двоичное число = 10000110, имеющее

а) шестнадцатиричный эквивалент = 86(HEX),

б) восьмиричный эквивалент = 206(OCT),

в) десятичный эквивалент числа без знака = 134(DEC),

2) дополнительный код отрицательного числа =-122(DEC),

3) двоично-десятичное упакованное число = 86(BCD),

4) альтернативный код буквы "Ж",

4') код КОИ-8 символа "¦",

5) восьмисегментный код цифры "1.",

6) часть вещественного числа,

7) реализация множества,включающего 3 элемента из 8-ми,

8) часть адреса ячейки памяти или внешнего устройства,

9) код операции и т.д.

Поэтому ответственность за интерпретацию двоичных наборов возлагается на программиста. Например, попытка сложить ASCII коды "1" + "2" не даст в сумме код "3", а даст 31(HEX) + 32(HEX) = 63(HEX), что соответствует коду латинской буквы "c".

Приложение № 2

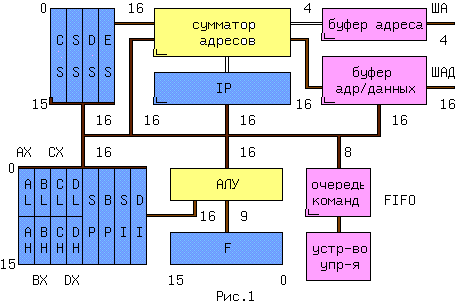

СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРА

Огромное количество микропроцессоров (МП) не позволяет рассмотреть их особенности, поэтому выбор пал на родоначальника семейства 80x86 : МП К1810ВМ86/88 (8086/8088). Такой выбор оправдан, во-первых преобладающим парком ЭВМ с этим МП, во-вторых тем, что все МП этого семейства при включении начинают работу в реальном режиме МП 8086, и в-третьих - программной совместимостью их ассемблеров снизу вверх. На рис 1. приведена структурная схема МП8086 и внешний вид типового микропроцессора.

Устройство управления декодирует байты программы и управляет работой операционного устройства и шинного интерфейса. Операционное устройство МП состоит из 4-х шестнадцатиразрядных регистров общего назначения: РОН (AX,BX,CX,DX), из 4-х регистров указателей (адресных регистров SP,BP,SI, DI) и арифметико-логического устройства (АЛУ) с регистром признаков операций (флагов F).

РОН служат для хранения промежуточных результатов операций, т.е. операндов. Помимо общих, каждый из этих регистров имеет и некоторые специальные функции, о которых будет сказано далее. Каждый РОН может раcсматриваться, как состоящий из двух независимых 8-ми разрядных регистров AH, AL, BH, BL, CH, CL и DH, DL.

Адресные регистры хранят 16-ти битовые указатели (адреса) на области памяти. В SP (StackPointer) находится текущий адрес "вершины стека" - специально организованной области памяти, которая будет описана далее. Регистр BP(Base Pointer) хранит любой базовый адрес в области стека. Два регистра SI и DI (Source и Destination Index) адресуют области памяти, называемые источником и приемником данных.

Шинный интерфейс, на рис.1 его узлы отмечены двойной чертой, выполняет операции обмена между МП и памятью или внешними устройствами. В сегментных регистрах CS,SS,DS,ES хранятся указатели на 64-х килобайтные области памяти называемые сегментами. Значения этих указателей могут перекрываться. Адрес байта в ячейке памяти получается суммированием содержимого одного из сегментных регистров и одного из регистров (SP,SI,DI,IP). Например адрес текущего байта программы, извлекаемого из памяти определяется суммой адресов, хранящихся в регистре кодового сегмента (CS) и указателе команд (IP). В регистре IP хранится 16-битовый адрес байта в кодовом сегменте к которому микропроцессор дожен обратиться. Подробнее об этом будет сказано далее. Связь с внешними устройствами осуществляется через специальные тристабильные схемы с повышенной нагрузочной способностью и называемые буферами.

Текущий байт программы направляется в очередь команд: шесть однобайтовых регистров расположенных конвейером (по принципу "первым вошел - первым вышел" или FIFO ). Конвейер позволяет одновременно выполнять команду из очереди и загружать следующую, повышая производительность МП. Буферные тристабильные элементы увеличивают мощность сигналов до стандартных значений ТТЛ.

8.2 РЕГИСТР ФЛАГОВ

По результатам операций АЛУ устанавливает либо сбрасывает отдельные биты в регистре флагов F.

![]()

x обозначает, что содержимое этого бита не имеет значения. Некоторые операции влияют только на отдельные флаги, а другие совсем на них не воздействуют, поэтому при описании флагов подразумевается выполнение тех команд (операций), которые влияют на эти флаги. В дальнейшем, в тексте, фраза "содержимое XX" будет обозначаться круглыми скобками - (XX).

- ZF - флаг/признак нулевого результата (Zero), устанавливается в 1, если получен нулевой результат, иначе (ZF)=0.

- CF - флаг переноса (Carry) устанавливается, если в результате выполнения операции из старшего бита переносится или занимается 1 при сложении или вычитании, иначе (CF)=0. На CF влияют также команды сдвига и умножения.

- SF - флаг знака результата (Sign) равен единице, если результат отрицательный, т.е. он дублирует старший знаковый бит результата.

- PF - флаг четности (Parity). (PF)=1, если сумма по модулю два всех битов результата равна нулю (число единичных битов - четное).

- AF - флаг дополнительного переноса (Auxiliary) устанавливается, если есть перенос из старшего бита младшей тетрады (бит D3) в младший бит старшей тетрады (бит D4). Используется в операциях над упакованными BCD числами.

- OF - флаг переполнения (Overflow) устанавливается, когда результат операции превысит одно- или двухбайтовый диапазон чисел со ЗНАКОМ, а также в некоторых других случаях. Другое определение: (OF)=1, если перенос/заем в старший бит результата не равен переносу/заему из старшего бита.

Рассмотрим в качестве примера сложение двух однобайтовых чисел: 125 + 4 = 129 выходит за пределы -128.. ..+127 чисел со знаком (для беззнаковых чисел 129 - корректный результат).

0 1 1 1 1 1 0 1 = +125

0 0 0 0 0 1 0 0 = +4

1 0 0 0 0 0 0 1 = +129 > +128 (или -127 ???)

/ / :

0 1 :

Перенос в бит D7 равен 1, а из бита D7 = 0, в результате сложения чисел (OF) = 1, (CF) = 0, (ZF) = 0, (SF) = 1, (PF) = 0, (AF) = 1. Остальные три флага будут рассмотрены далее. Содержимое регистра признаков называется также словом состояния процессора(программы) и обозначается PSW.

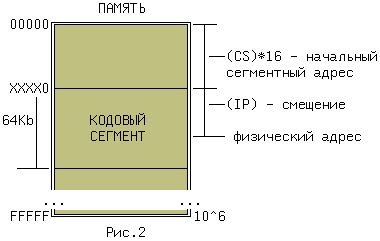

ОРГАНИЗАЦИЯ ПАМЯТИ И ВЫЧИСЛЕНИЕ АДРЕСА

МП 8086 имеет 20-ти разрядную шину адреса ША, позволяющую обращаться к 2^20 или примерно к одному миллиону ячеек памяти. 16-ти битовая шина данных ШД может пересылть информацию байтами или словами. Память обычно организована в виде линейного одномерного массива байтов, причем два соседних байта могут рассматриваться как слово. Все мегабайтное пространство памяти условно делится на 16 сегментов объемом по 64Kb. Микропроцессору доступны в каждый момент четыре - кодовый сегмент, где хранится программа, стековый сегмент, сегмент данных программы и дополнительный сегмент данных. Начальные адреса этих сегментов хранятся в регистрах CS,SS,DS и ES. Так как эти регистры 16-ти битовые, а все адресное пространство 20-ти битовое, то МП начальный сегментный адрес в 20-ти битовом сумматоре сдвигает на четыре бита влево (эквивалентно умножению на 16) и складывает с содержимым одного из регистров (IP,SP,DI,SI).

Полученное число называется физическим адресом. Например, извлекая из памяти очередной байт кода программы МП формирует физический адрес по формуле: Физический адрес = (IP) + (CS) * 16, где (IP) - смещение, эффективный или исполнительный адрес, (CS) - сегментный адрес, а (CS) * 16 - называется начальным сегментным адресом. Организация памяти приведена на рис.2.

8.4 ПРОЦЕССОРНЫЙ БЛОК (ПБ )

включает микропроцессор, стабилизируемый кварцем генератор импульсов, два устройства для формирования адресных и управляющих сигналов и двунаправленный буфер шины данных. Схема ПБ представлена на рис.3. Для уменьшения общего количества выводов МП, по некоторым из них в разные моменты передаются разные сигналы, поэтому младшие 16 линий адреса и шина данных совмещены (мультиплексированы).

Конденсатор C до включения питания разряжен. В начальный момент времени t0 подается напряжение питания на выводы (+). Начиная с этого момента времени на входе ~RES действует логический 0 до момента t1, когда напряжение на конденсаторе C достигнет порогового значения логической 1. В течение интервала t0..t1 выходной сигнал RESET имеет активный уровень лог.1. Микропроцессор переводится в исходное состояние. При этом в регистр CS записывается код FFFFh, а в регистр IP код 0000h.

Когда C зарядится и сигнал ~RES станет "1", на входе RESET микропроцессора сигнал снизится до пассивного уровня. Начинается основной цикл работы. МП извлекает из ячейки памяти с адресом FFFF:0000 первый байт команды, который чаще всего является кодом безусловного перехода к тому месту в памяти, где находится начало программы. В процессе работы можно перезапустить МП с помощью кнопки SW. Конденсатор C разряжается до нуля и процесс запуска повторяется. МП может работать в двух режимах в максимальном и минимальном. Минимальный режим ограничивает адресуемый объем памяти до 64Kb. В большинстве приложений в приборостроении такого объема достаточно, поэтому сигнал ~MX/MN = 1. Формирователи сигналов ШУ,ША и ШД (шины управления адреса и данных), выполнены на элементах ИЛИ, регистрах и шинных формирователях и служат также для увеличения мощности этих сигналов.

Генератор G формирует последовательность импульсов CLK, называемых тактовыми. Выполнение команды производится в течение интервалов времени, называемых циклами. Если в цикле есть обращение к памяти или к внешним устройствам, то он называется циклом шины. Цикл шины содержит 4 обязательных такта T1 ... T4.

В такте T1 микропроцессор передает по совмещенной шине адрес/данные адрес ячейки памяти или внешнего устройства (ВУ), подключенного к шинам ШУ,ША и ШД. В такте T2 производится выбор направления обмена данными с памятью или ВУ, а в тактах T3,T4 - передача данных. Если ЗУ (запоминающее устройство) или ВУ медленные, то на вход готовности RDY посылается сигнал RDY = 0, по которому МП вставляет циклы ожидания TW, до тех пор, пока не будет установлена готовность ВУ или ЗУ (RDY = 1). Если в цикле нет обращения к шине, то МП формирует холостые циклы TI.

Для разделения сигналов совмещенной шины адрес/данные ШАД(AD15..0) их необходимо "демультиплексировать" с помощью регистра защелки адреса RG и двунаправленного буфера BD. При обращении к памяти (в том числе при выборке команды) микропроцессор передает по ШАД адрес ячейки памяти. Этот адрес записывается в D-триггеры регистра RG сигналом ALE генерируемым микрпроцессором в этот момент и поступающим на синхровходы D-триггеров. Адрес в регистре сохраняется на время последующей передачи данных. Следом по ШАД передаются, либо данные от микропроцессора к ВУ или ЗУ, либо в обратном направлении. МП должен, во-первых, обеспечить правильное направление передачи буфера BD и , во-вторых, открыть (разрешить) тристабильные элементы буфера для передачи данных. Первую задачу решает сигнал МП ~DT/R (~DT/R=0 передача данных от МП - Transmit, ~DT/R=1 прием данных МП - Receive).

Вторая задача решается генерацией МП сигнала ~DEN (Data Enable). Чтение или ввод данных в один из регистров МП осуществляется с помощью инверсных сигналов шины управления (ШУ): ~MEMR (чтение из памяти),~IOR (ввод из ВУ), называемыми еще стробами чтения. Запись или вывод данных из МП по шине данных сопровождается стробами записи ~MEMW (запись в память (ЗУ)), или ~IOW (вывод во внешнее устройство (ВУ)). Четверка стробов, которые являются основными сигналами шины управления, формируется из сигналов чтения, записи (~RD,~WR) и сигнала M/~IO, определяющего к чему производится обращение : к ЗУ или ВУ. Формирование этих сигналов производится с помощью простой комбинационной схемы, содержащей 4 элемента ИЛИ и один инвертор.

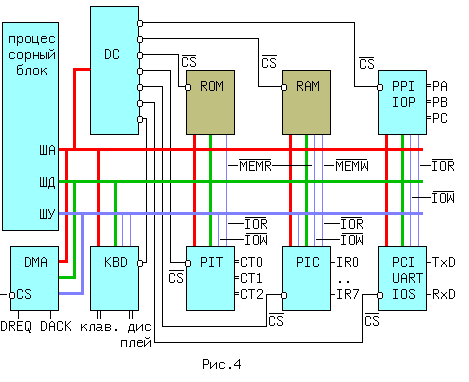

8.5 МИКРОПРОЦЕССОРНАЯ СИСТЕМА С ТРЕМЯ ШИНАМИ

Работой всех устройств подключаемых к процессорному блоку управляет дешифратор DC, к входам которого подводятся линии шины адреса. Обычно дешифраторов бывает несколько. Если используется не все адресное пространство для памяти и ВУ, то на дешифратор заводятся не все линии адреса, чаще всего несколько старших разрядов ША. Например, если на DC завести 4 линии A19..A16, то все адресное пространство будет разбито на неперекрывающиеся блоки по 2^20 / 2^4 = 64Кб, принадлежащие каждому из 16-ти (2^4 = 16) устройств ЗУ или ВУ, подключенных к шинам (на рис.4 показаны 7 устройств). Часть из них могут использовать все отводимое им адресное пространство, например ПЗУ и ОЗУ, другие только несколько адресов.

Типовая МПС, показанная на схеме содержит:

микросхему программируемого периферийного интерфейса ППИ (PPI или IOP), к которой через три 8-битовых независимых канала PA,PB и PC можно подключать периферийные устройства, например принтер, клавиатуру, 8-ми сегментный дисплей или ЦАП и АЦП. Через ППИ может производиться обмен данными с другими МПС или ЭВМ.

Ввод с клавиатуры и вывод на дисплей могут производиться специальными микросхемами.

Связь с удаленными устройствами или абонентами сетей может осуществляться с помощью универсального асинхронного последовательного приемо-передатчика УАПП-UART (программируемый связной интерфейс ПСИ-PCI или IOS). К выводам RxD - приемник и TxD - передатчик через линию связи подключаются передатчик и приемник другого абонента или устройства. Если связь производится через модем, то доступны любые сети.

Для формирования точных, различных по частоте и длительности сигналов, в т.ч. и звукового диапазона используется программируемый интервальный таймер ПИТ-PIT, имеющий три независимых 16-ти разрядных двоичных счетчика. Задержка, длительность или частота выходного сигнала каждого счетчика кратна 3..65535 периодам входного сигнала.

Если в системе используется режим прерывания выполнения основной программы внешними устройствами, требующими безотлагательного вмешательства микропроцессора, то может применяться программируемый контроллер прерываний ПКП - PIC (устройство собирающее заявки на обслуживание от ВУ с входов IRi). Подробно прерывания будут рассмотрены ниже.

Обмен данными между МП и ЗУ или одним из ВУ возможен только при появлении на выходе дешифратора DC единственного сигнала ~CS = 0, поступающего на то устройство с которым будет производиться запись или чтение байта данных. Остальные (невыбранные) устройства будут в пассивном состоянии, т.к. их сигналы ~CS = 1. Байт информации на ШД считывается ВУ, ЗУ или МП в строго ограниченном интервале времени во время действия одного из управляющих сигналов чтения/записи (~MEMR, ~MEMW) из памяти или в память, или во время действия одного из сигналов управления вводом/выводом (~IOR, ~IOW) в/из ВУ.

Быстрый обмен данными может производиться с помощью устройства прямого доступа к памяти ПДП (DMA).

8.6 СТЕК

Область памяти с упрощенной схемой адресации, к которой МП обращается по принципу "последним вошел - первым вышел" (LIFO). Байты программы в оперативной памяти располагаются последовательно по нарастающим адресам. Стек заполняется по последовательно убывающим адресам. Во избежание перекрытия этих двух областей памяти стек обычно располагается в старших адресах. Начальный адрес стека, называемый дном (bottom) записывается в регистр SP командой MOV SP,0fffeh. Вместо 0fffeh - адрес предпоследнего байта сегмента, может быть другое значение, но выравненное по двухбайтовым, т. е. четным адресам. Текущее значение содержимого SP называется, также адресом вершины стека (top). Если адрес вершины совпадает с адресом дна - стек считается пустым. Рассмотрим механизм помещения в стек и извлечения из него данных на примере команд PUSH AX и POP BX. Пусть начальное значение аккумулятора AX равно 874c.