Реферат: Разработка программы на Ассемблере

Реферат: Разработка программы на Ассемблере

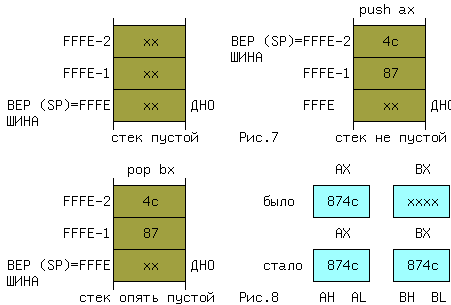

Команда PUSH выполняется в четыре этапа:

- Адрес в SP уменьшается на 1: (SP) <-- (SP) - 1.

- По этому адресу помещается старший байт 87: ((SP)) <-- (AH).

- Содержимое SP снова уменьшается на 1: (SP) <-- (SP) - 1.

- По полученному адресу загружается младший байт 4c: ((SP)) <-- (AL).

Действие команды POP аналогично описанному процессу, но в происходит в обратном порядке:

- (BL) <- ((SP)),

- (SP) <- (SP) + 1,

- (BH) <- ((SP)),

- (SP) <- (SP) + 1.

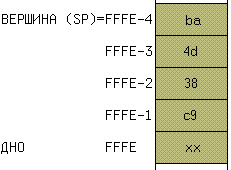

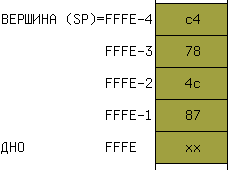

Байты в стек помещаются по правилу "старший байт по старшему адресу" . На рис.7 показан пустой стек до выполнения команды PUSH AX и после ее выполнения, а на рис.8 после выполнения команды POP BX.

Преимущество стека в том, что программисту не нужно заботиться об абсолютных значениях адресов переменных, но в этом таится и опасность, если текущее содержимое указателя стека будет потеряно, при неаккуратных действиях программиста, то работа компъютера станет непредсказуемой и он, как говорят в таких случаях, "зависнет". В программах стек используется для:

1) сохранения и извлечения адреса возврата из подпрограмм командами ассемблера CALL и RET (IRET),

2) хранения локальных переменных,

3) передачи фактических параметров подпрограммам (трансляторами с языков высокого уровня),

4) временного хранения содержимого регистров фоновой программы при ее прерывании.

8.7 СПОСОБЫ ВВОДА-ВЫВОДА

Обмен данными между ЭВМ и ВУ или ЗУ называется вводом-выводом (ВВ). Существует четыре основных способа ВВ.

- Программный ВВ

- ВВ по прерываниям

- Прямой доступ к памяти (ПДП) или DMA

- Транзакции (MCS-96)

В первых двух случаях в обмене данными участвует микропроцессор. В режиме ПДП функции управления обменом берет на себя специальное устройство - контроллер ПДП, причем МП в это время в обмене данными не участвует. В 4-ом способе пересылки производятся параллельно с работой МП периферийным сервером транзакций.

8.7.1 ПРОГРАММНЫЙ ВВОД-ВЫВОД

Для внешних устрйств выделяеся адресное пространство, либо не входящее в состав ЗУ, либо являющееся его частью. Следовательно программный ВВ может быть двух типов:

- с помощью команд ассемблера ввод (IN) и вывод (OUT)

- с использованием всех команд пересылки ассемблера (MOV, LODSB,..).

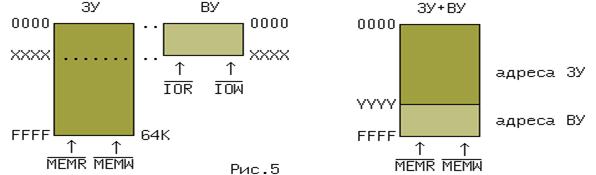

В пределах 64K блока карта распределения памяти для первого случая показана на рис.5 слева.

В пределах интервала 0000 ...XXXX адреса ВУ и ЗУ пересекаются. Поэтому для однозначного обращения к ячейкам памяти или ВУ в процессорном блоке формируются управляющие пересылкой стробирующие импульсы - ~IOR,~IOW для ввода или вывода данных во внешнее устройство и ~MEMR,~MEMW для чтения или записи в память.Емкость ЗУ для размещения программ и данных не уменьшается.

Карта распределения памяти для второго случая показана на рис.5 справа. Под внешние устройства выделяется часть адресного пространства ЗУ. Емкость ЗУ уменьшается на количество адресов отводимых для ВУ. Второй способ позволяет адресоваться к ВУ с помощью всех команд оперирующих с памятью. Основное достоинство программного ВВ в простоте. Но при выполнении ввода, например с клавиатуры, МП затрачивает до 99,99..% времени на ожидание, не выполняя при этом другой полезной работы. Избавиться от этого недостатка позволяет ВВ по прерываниям.

8.7.2 ВВОД-ВЫВОД ПО ПРЕРЫВАНИЯЮ

В общем случае прерывания могут вызываться

- внешнними устройствами (внешние прерывания),

- командами прерываний (программные прерывания)

- автоматически самим МП (внутренние прерывания), например при попытке деления на 0.

В этом разделе будут рассмотрены внешние прерывания. Работу МП можно разделить во времени между двумя независимыми программами: фоновой, которая выполняет основную задачу и программой ВВ данных. Когда ВУ подготовит данные для передачи, оно посылает сигнал запроса на прерывание непосредственно на вход МП INTR или в специальное устройство - контроллер прерываний. В процессе обслуживания прерывания выполняются следующие действия:

1. ВУ самостоятельно, либо через контроллер прерываний посылает сигнал прерывания INT(R) на одноименный вход МП;

2. МП завершает выполнение текущей команды и,если преывания разрешены командой ассемблера STI(EI для 8085), то подтверждает разрешение сигналом ШУ -INTA;

3. В МП по ШД передается тип(номер) прерывания - N;

4. Содержимое PSW, а также CS,IP (адрес возврата), скорректированное с учетом сброса очереди помещается в стек;

5. Сбрасываются флаги IF (флаг разрешения прерываний) и TF (флаг трассировки), причем т.к. (IF) = 0 дальнейшие прерывания запрещаются;

6. В IP загружается содержимое двух байтов с начальным адресом 4*N, а в CS - содержимое следующих двух байтов . Эти 4 байта называются вектором (указателем) прерывания.

7. Начинает выполняться подпрограмма - обработчик прерывания.

INT_SUBR:

STI

PUSH AX

....; здесь

....; команды

MOV AL,5; обработчика

....; прерывания

....

POP AX

IRET

Если допускаются вложенные прерывания, то вначале помещается команда STI- разрешение преываний, запрещенных в п.5. Инструкции push и pop сохраняют и восстанавливают содержимое регистров фоновой задачи, если эти же регистры используются и обработчиком прерывания (в примере регистр AX).

8. Команда IRET извлекает из стека адрес возврата - IP,CS и содержимое PSW;

9. МП прдолжает работу с адреса возврата. При выполнении программных прерываний по команде INT N действия выполняются с п.3. N находится в пределах 0 <= N <= 255, поэтому четырехбайтовые вектора прерываний занимают первые 1024 байта памяти.

8.7.3 ПРЯМОЙ ДОСТУП К ПАМЯТИ (ПДП) И ТРАНЗАКЦИИ

Обмен большим количеством байтов, между ВУ (например дисковым накопителем) и памятью с помощью предыдущих двух методов малоэффективен, т.к. обмен происходит по цепочке: ВУ - аккумулятор (AX или AL) - память или наоборот. В режиме ПДП при поступлении запроса от ВУ на вход HOLD, МП разрешает обмен выходным сигналом HLDA. Микропроцессор на время обмена отключается от ШУ,ШД и ША переводя их в третье состояние по входам ~OE буферных элементов сигналом ~BUSEN = 1 .Специальная микросхема (контроллер ПДП) использует освободившиеся шины для высокоскоростного прямого обмена ВУ - память. Скорость обмена достигает многих мегабит/сек.

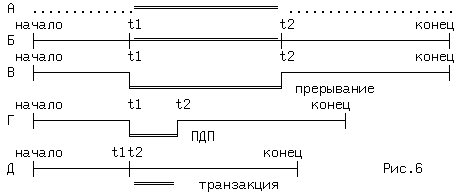

На рис.6 показан процесс выполнения основной (фоновой) программы - интервалы времени (начало..t1, t2..конец) и выполнение процедуры передачи массива данных, на рисунке этот отрезок времени обозначен двойной линией. На диаграмме (А) ЭВМ задействована только для передачи (отрезок t1..t2), в остальное время компьютер бездействует. Во втором варианте - диаграмма (Б), код программы передачи жестко встроен в фоновую задачу. В третьем варианте (В) передача массива оформлена в виде подпрограммы прерывания, причем если запроса на прерывание не поступит,то суммарное время на выполнение фоновой программы уменьшится на t2-t1. При использовании режима ПДП сохраняются преимущества метода прерывания, время на передачу сокращается - диаграмма (Г), но фоновая задача по прежнему прерывается. В последнем случае передача данных производится почти без нарушения хода программы параллельно во времени (Д). Транзакции реализованы в некоторых семействах однокристальных микроЭВМ например в MCS-96.

ЗАДАЧИ И УПРАЖНЕНИЯ

Одна подпрограмма вызывает другую.Укажите короткий адрес возврата из вложенной прoцедуры.

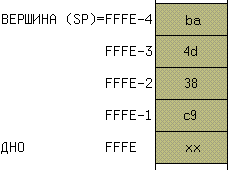

Пояснение : Вложенная подпрограмма это подпрограмма, которая вызывается из другой подпрограммы. Вызов подпрограммы сопровождается помещением в стек адреса возврата. Стек заполняется начиная с дна. Короткий адрес - двухбайтовый адрес в пределах одного кодового сегмента. Байты в стек помещаются по правилу "старший байт по старшему адресу". Теперь нетрудно ответить на предложенный вопрос: 4dba.

В тексте программы следуют подряд команды: PUSH AX; PUSH CX; POP DX; POP BX. Чему будет равно содержимое регистра BH? Рисунок стека соответствует промежуточному состоянию (до выполнения команд POP).

Пояснение : В стек дважды что-то помещается и дважды что-то извлекается, причем последние два байта помещаются в регистр BX. Перефразируя правило "последним вошел - первым вышел" в "последним вышел - первым вошел", придем к выводу, что содержимое AX засылается в регистр BX. Команда PUSH AX помещает два байта в стек по правилу "старшая половина двухбайтового регистра - по старшему адресу". Ответ: c9

В тексте программы следуют подряд команды: POP AX; POP DX. Чему будет равно содержимое регистра DL?

Ответ: 4c

На временных диаграммах внизу приведены управляющие сигналы на выходах микропроцессора (без сохpанения точных вpеменных пpопоpций). Что осуществляется в момент времени отмеченный знаком + ? Чтение данных из памяти, запись данных в память вывод данных в порт, ввод данных из порта, ничего из указанного выше.

Пояснения : Если ~DEN=0 (разрешение данных) возможно 4 случая (для приведенных диаграмм): 1) M/~IO = 0, ~RD = 0 активны сигналы ввод/вывод (~IO) и чтение-ввод (~RD). 2) M/~IO = 0, ~WR = 0 активны сигналы ввод/вывод (~IO) и запись-вывод(~WR). 3) M/~IO = 1, ~RD = 0 активны сигналы обращения к памяти(M) и чтение-ввод(~RD). 4) M/~IO = 1, ~WR = 0 активны сигналы обращения к памяти(M) и запись-вывод(~WR).

Ответ: Вывод данных в порт.

Приложение № 3

ОСНОВНЫЕ ПОЛОЖЕНИЯ АЛГЕБРЫ ЛОГИКИ

В отличие от аналоговых электронных устройств, в цифровых устройствах (ЦУ) входные и выходные сигналы могут принимать ограниченное количество состояний. В соответствии с логическим соглашением (ГОСТ 2.743-82), в зависимости от конкретной физической реализации элементов ЦУ, более положительному значению физической величины, "H" - уровень, соответствует состояние "логическая 1", а менее положительному значению ,"L - уровень" - "логический 0". Такое соглашение называется положительной логикой. Обратное соотношение называется отрицательной логикой. В ГОСТ'е 19480 - 89 даны наименования, определения и условные обозначения основных параметров и характеристик цифровых микросхем.

Теоретической основой проектирования ЦУ является алгебра-логики или булева алгебра, оперирующая логическими переменными. Для логических переменных, принимающих только два значения,существуют 4 основных операции. Операция логическое "И" (AND) конъюнкция или логическое умножение, обозначается * или /\. Операция логическое "ИЛИ" (OR), дизъюнкция или логическое сложение, обозначается + или \/ . Операция логическое "НЕ" (NOT), изменение значения, инверсия или отрицание, обозначается чертой над логическим выражением. Инверсия иногда будет в тексте обозначаться знаком " ~ ". Операция эквивалентности обозначается "=" . Следующие соотношения являются аксиомами.

| (1) | 0 + 0 = 0 | 1 * 1 = 1 | (1') | |

| (2) | 1 + 1 = 1 | 0 * 0 = 0 | (2') | |

| (3) | 1 + 0 = 0 + 1 = 1 | 0 * 1 = 1 * 0 = 0 | (3') | |

| (4) | ~1 = 0 | ~0 = 1 | (4') |

Из (1, 2) и (1',2') следует: x + x = x и x * x = x. (5)

Из (1, 3) и (2',3') следует: x + 0 = x и 0 * x = 0. (6)

Из (2, 3) и (1',3') следует: 1 + x = 1 и x * 1 = x. (7)

Из (3) и (3') следует: x +~x = 1 и~x * x = 0. (8)

Из (4) и (4') следует: ~(~x) = x. (9)

И, наконец, из (1,1'), (2,2'), (3,3') и (4,4') следует:

~( x0+x1 ) = ~x0 * ~x1 и ~( x0 * x1) = ~x0 + ~x1 . (10)

Последние выражения (10) называют принципом двойственности или теоремой Де Моргана (инверсия логической суммы равна логическому произведению инверсий и наоборот). Соотношения двойственности для n переменных, часто записывают в виде:

~(x1 + .. + xn) = ~x1 * . .* ~xn и

~(x1 * .. * xn) = ~x1 + .. + ~xn (11)

На функции И и ИЛИ распространяются обычные алгебраические законы - переместительный, сочетательный и распределительный, которые легко доказываются методом перебора: x1 op x0 = x0 op x1 - переместительный, x2 op x1 op x0 = (x2 op x1) op x0 - сочетательный и x2*(x1+x0) = (x2*x1) + (x2*x0) и x2 + (x1*x0) = (x2+x1) * (x2+x0) - распределительный, где операция op может быть, либо И, либо ИЛИ. Наряду с тремя основными логическими функциями, называемыми также переключательными, существуют и другие.

1.2 ПЕРЕКЛЮЧАТЕЛЬНЫЕ ФУНКЦИИ

Для n - логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции 0 или 1. Если значения функции отличаются хотя бы на одном наборе, функции - разные. Общее число переключательных функций (ПФ) от n аргументов равно N=22n. Для n=2, N=16. При n=3, N=256 и далее очень быстро растет. Практическое значение имеют 16 функций от 2-х переменных, т.к. любое сложное выражение можно рассматривать как композицию из простейших. В таблице 1 приведены некоторые из ПФ для n=2. i-номер набора входных переменных x1 и x0.

ЗАПОМНИТЕ СЛЕДУЮЩИЕ ОПРЕДЕЛЕНИЯ. Функция "И" равна единице, если равны единице ВСЕ ее аргументы. Функция "ИЛИ" равна единице, если равен единице ХОТЯ БЫ один аргумент. Функция "ИСКЛЮЧАЮЩЕЕ ИЛИ" (XOR) равна единице, если равен единице ТОЛЬКО один ее аргумент.

1.3 УСЛОВНЫЕ ОБОЗНАЧЕНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ НА СХЕМАХ

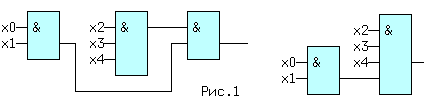

Количество входов логического элемента, участвующих в формировании логической функции, называется коэффициентом объединения - Коб ( не путать с коэффициентом разветвления). У всех выше приведенных схем, за исключением инвертора, коэффициент объединения равен двум. Промышленностью выпускаются схемы с Коб=2,3,4,8. Для получения схем с другим числом входов основные элементы можно объединять. Например, если требуется пятивходовая схема И, то ее можно получить, используя сочетательный закон следующим способом: x0 * x1 * x2 * x3 * x4 = (x0*x1) * (x2*x3*x4) = (x0*x1) * x2 * x3 * x4, т.е. требуются две двухвходовые и одна трехвходовая схемы И, для первого варианта, либо одна двухвходовая и одна четырехвходовая - для второго (рис.1).

Можно использовать и восьмивходовую схему И, подав на незадействованные входы "1", либо некоторые из переменных, в соответствии с выражениями (5) или (7).